用于减二的组合电路二进制数被称为减法器。当单个位的二进制数是减去,然后,我们可以使用半减法器来完成任务,而如果我们需要减去三个二进制数的一位(其中两个通常会被输入,另将借),我们将不得不使用满减法器。现在如果我们要减去两个n位的二进制数呢?这种情况需要使用n位平行减法器。

平行减法器的结构

一般来说,当需要用二进制数1减去二进制数2时,二进制数2将用its表示2的补形式,然后与二进制数1相加(只有2的补码形式)二进制减)。

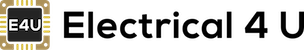

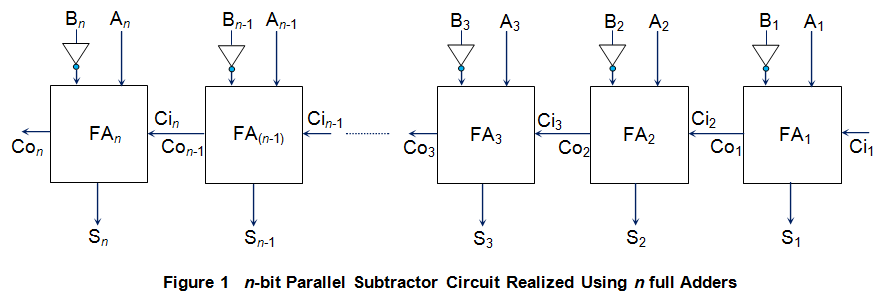

接下来,2的一个数字的补码可以通过计算得到1的补然后在其最低有效位(LSB)上加1。而且,取1的补码只是表示对二进制数。从讨论中,我们可以得出这样的结论:为了完成减法,我们可以使用与加法相同的电路。并行加法器”),前提是我们有“要减”的数字2的补码形式。表示数字的任务2的补形式可以通过初次使用而产生不是盖茨对二进制数中的位进行反运算。然而,要在LSB上加1,可以使用n序列中的第一个加法器完整的方案在电路中仅通过在进位时提供高电平逻辑(Ci1销。因此,我们可以设计n位平行减法器如图1所示。

在这里,二进制数 被除数和二进制数是多少

被除数和二进制数是多少 是减数。此外,每个加法器的和输出实际上对应于差分位(预期结果),而最后的执行引脚完整的加法器(有限公司n)只不过是由此而来的借贷。

是减数。此外,每个加法器的和输出实际上对应于差分位(预期结果),而最后的执行引脚完整的加法器(有限公司n)只不过是由此而来的借贷。

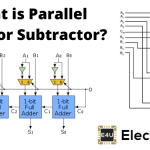

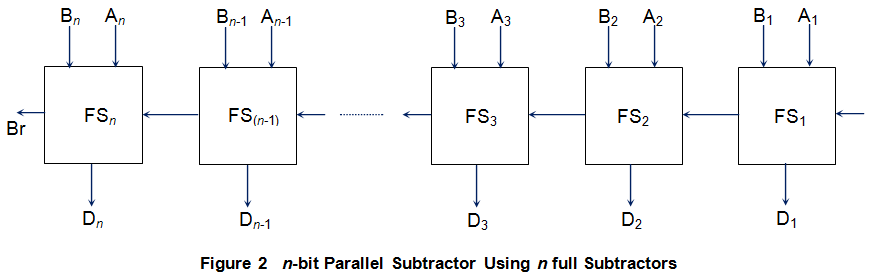

除了这种电路外,我们甚至可以用全减法器的级联阵列来设计并联减法器。图2显示了使用n个全减法器设计的这种an-bit并行减法器(FS1对FSn)连接方式类似于n位并行加法器的连接方式。

这种电路的工作原理是直接的,与a电路的工作原理非常相似并行加法器。结果,甚至平行减法器容易受到纹波传播的影响,导致输出延迟。也就是说,如果与每个完整减法相关联的dealy是T秒,那么总体差位(D1D2D…n)和借位(Br)仅在n T秒后获得。