转移寄存器可分为两种类型,即静态移位寄存器和动态移位寄存器。静态移位寄存器由拖鞋并能在其中无限期地储存信息。另一方面,动态移位寄存器由动态逆变器组成,并采用临时电荷存储技术,因此需要频繁刷新周期来存储数据。

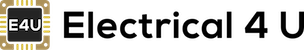

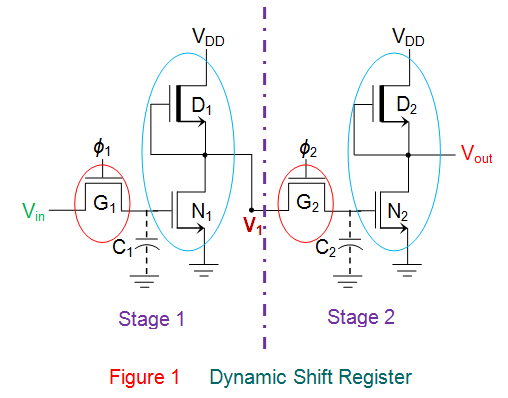

图1显示了由NMOS传输门(红色圈出的元件,G1和G2)和NMOS消耗模式逆变器(蓝色圈出的组件,{D1N1}和{D2N2})。这里φ.1和ϕ2均为非重叠、互补的时钟信号,而C1和C2分别表示阶段1和阶段2的栅极到源极电容。更多这些功放在初始状态下,电荷被耗尽。

现在考虑V.在= 0V and ϕ1= VDD,其分别对应于逻辑状态0和1。对于这种情况,门G1将是开放的(不导电的),因此电容器C1会保持它的未带电状态。

这将导致输出电压阶段1中的逆变器电路的水平(由D形成1和n1)走高即将v1= VDD(为简单起见,假设电路中所有设备的阈值电压为零)。然而对于这个,ϕ1由于电容器的充电是一个渐进的过程(考虑到RC时间常数问题),因此在足够的时间内保持其高状态。现在如果ϕ2走高,然后是门g2由于电容器C关闭2开始通过它逐渐充电到电压等级VDD(= V1),对使用时钟频率的限制施加。此外,应注意,作为电容器C两端的电压2增加,由于通过d形成的电路的反相动作,级2处的输出电压降低2和n2。这进而导致输出电压V出降低电压(= 0V)。因此,可以说,V的状态在转移到v出。

同样如果V在= VDDwhileφ.1= VDD,那么C1费用到VDD通过G1引起第1级输出电压V1要低。此时如果ϕ2= VDD,则G门2闭合,电容器C2当输出电压V时放电出逐渐增加。这样就得到了V出= VDD,反映输入的逻辑高状态电压。因此,V的状态在反映在v出,这意味着V在转移到v出在时钟的控制下。这意味着图1所示的电路充当单级移位寄存器。然而,一个n级动态移位寄存器可以通过级联n个级来设计。

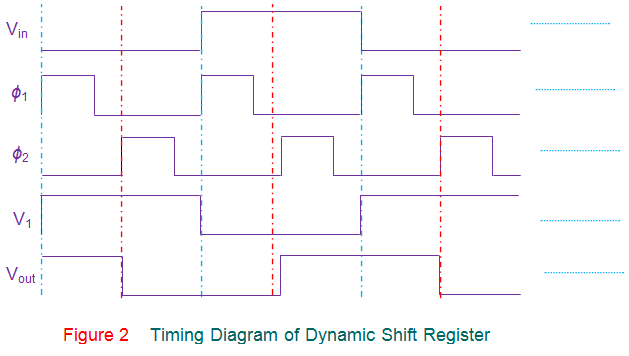

单级工作动态移位寄存器可以通过图2所示的时序图进一步强调。

从解释中可以清楚地看出,动态移位寄存器以电荷的形式存储在电子(特别是MOS)器件的栅-基板寄生电容上的信息。然而,这种充电容易发生泄漏,因此需要定期刷新数据,以确保存储的数据的逻辑级别是无错误的。这一目标是通过不断地将数据从一个阶段转移到另一个阶段,同时将最后一个阶段的输出返回到第一个阶段来实现的。这意味着动态移位寄存器必须在最小时钟频率下操作。

动态移位寄存器由于尺寸较小,在制造方面比较简单,并且具有较高的封装密度。然而,值得注意的是,它们的低功耗的优势被耗电量随着频率的增加而增加的事实所诅咒。此外,在动态移位寄存器的情况下,还有许多设计变体可用,如使用增强负载的动态移位寄存器,使用CMOS器件的动态移位寄存器等,包括比率逻辑方法和少比率逻辑方法。然而,基本的工作原理是一样的。