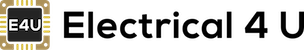

什么是pn结?

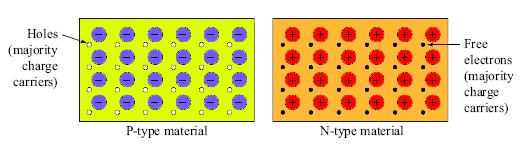

一种PN结(或者pn结)被定义为在半导体的单晶内的两种类型的半导体材料(p型和n型半导体)之间的界面。正(“P”)侧含有过量的孔,而负(“N”)侧侧包含过量的半导体内原子的外壳中的电子。

当N型材料与产生半导体的p型材料一起融合时,形成PN结。二极管。

我们可以创建一个PN结通过连接面部面对一个p型和一个n型半导体通过特殊技术晶体块。更实际地,我们可以通过通过三价杂质和由五价杂质掺杂半导体晶体的一侧和另一侧的一侧来形成P n结。

形成了我们掺杂三价杂质的半导体晶体的一侧P型半导体以及我们掺杂五价杂质的半导体晶体的一侧形成了n型半导体。

这些p型和n型半导体的晶体的中间部分满足形成为p-n结的典型连接。

由于该结,半导体晶体块得到典型的电压电流特性。该电压 - 电流特性是所有半导体元件的基础。

如何制作PN交界处

现在,让我们检查如何创建该PN结。p型半导体中有很多孔,n型半导体中有大量的自由电子。

同样在p型半导体中,有许多三价杂质原子,理想情况下,p型半导体中的每个空穴都与一个三价杂质原子相连。

这里我们用理想这个词是因为我们忽略了晶体中热产生的电子和空穴。现在如果一个电子位于一个空穴上,与空穴相关的杂质原子就变成了负离子。

因为它现在包含了一个额外的电子。当三价杂质原子接受电子并带负电荷时,该杂质称为受体杂质。杂质原子取代了相同数目的半导体原子在晶体中并将自己置于晶体结构中。

因此,杂质原子在晶体结构中是静态的。当这些三价杂质原子接受自由电子而成为负离子时,离子保持静止。类似地,当半导体晶体掺杂五价杂质时,每一种原子杂质取代半导体原子的晶体结构;因此,这些杂质原子在晶体结构中变成静态的。

晶体结构中的每个五价杂质原子在最外面的轨道中具有一个额外的电子,它可以容易地作为自由电子拆卸。当它去除电子时,它变得带正电的离子。

随着五价杂质原子捐给半导体晶体的作为电子,杂质杂质被称为供体杂质。在此期间PN交界处的讨论,我们讨论了静态受体和给体杂质原子,因为它们在PN结的形成中起主要作用。

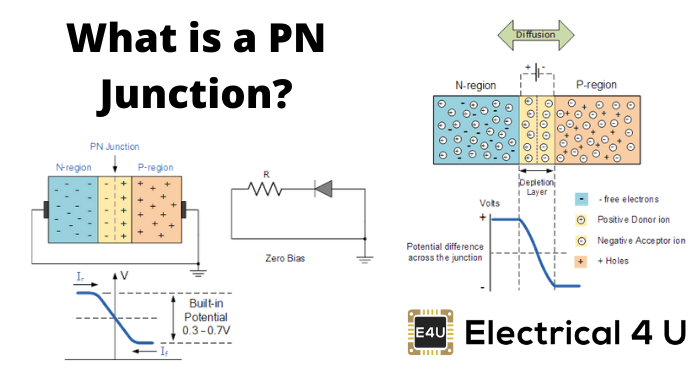

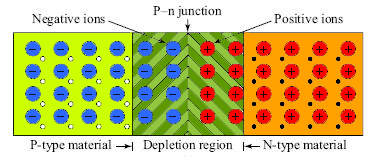

让我们来到一个点P型半导体与一个接触n型半导体,N型半导体上的自由电子更靠近结结,首先由于扩散而首先迁移到P型半导体,因为在n型区域中的自由电子浓度比p型区域的浓度大得多。

电子来到P区域将与他们首先找到的孔结合。这意味着自由电子来自n型区域将与接近结合的受体杂质原子结合。这种现象产生负离子。

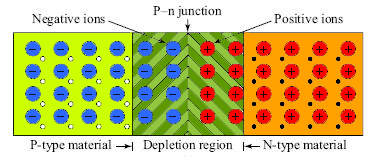

在p型区靠近结的受体杂质原子成为负离子时,在邻近结的p区会出现一层负的静态离子。

n型区域的自由电子首先迁移到p型区域,而n型区域的自由电子首先迁移到远离结的p型区域。这使得在邻接的n型区域有一层静态正离子。

在n型区域形成足够厚的正离子层和p型区域形成负离子层后,由于在自由电子前有一个负壁,电子不再从n型区域向p型区域扩散。这两层离子都来自PN结。

由于一层是带负电的,并且其他是正电荷的,则在结时会有电势,并且结合的表现类似于潜在的屏障。屏障电位取决于半导体材料,掺杂量和温度。

发现锗半导体的阻挡电位为0.3伏特25O.C,它在相同温度下用于硅半导体0.7伏。

这个势垒不包含任何自由电子或空穴,因为所有的自由电子都是在这个区域与空穴结合的,并且是由于空穴的耗尽航空公司收取(电子或孔)在该区域中,它也被称为耗尽区。虽然自由电子和孔的扩散在产生某些厚的耗尽层之后停止,但实际上,这种耗尽层的厚度在一系列微量测量中非常小。