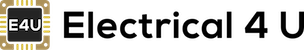

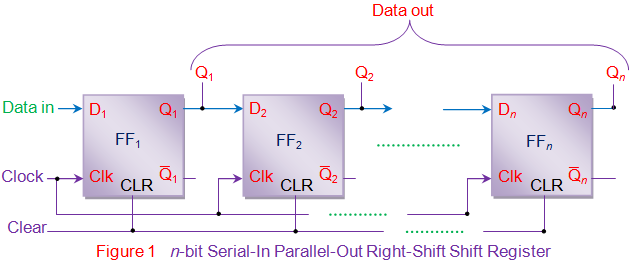

在串行进并行出(SIPO)移位寄存器时,数据以串行方式存储到寄存器中,而以并行方式从寄存器中检索数据。图1显示了一个n位同步SIPO移位寄存器对时钟脉冲的正边缘敏感。在这里,要存储的数据字(数据输入)是在第一个字的输入处串行输入的触发器(D1FF的1)。也可以看到,所有其他触发器的输入(除了第一个触发器FF1)是由前面的输出驱动的,例如,FF的输入2是由FF的输出驱动的1。在这种情况下移位寄存器,存储在寄存器内的数据作为并行输出数据字(数据输出)在触发器(Q1要问n)。

通常,在初始阶段通过在所有触发器的clear pin上应用high来清除寄存器内容。在这之后,第一个比特,B1在输入数据的D1销的FF1。

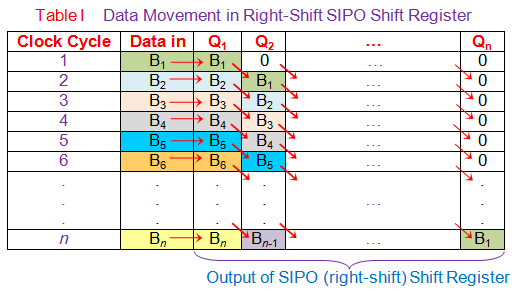

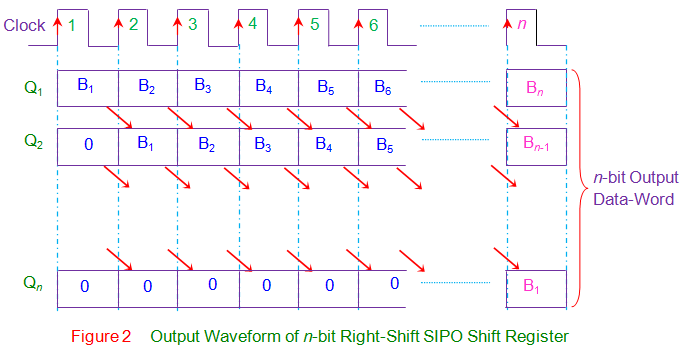

这一点(B1)将进入FF1,存储并因此出现在输出Q处1关于时钟第一个前缘的外观。在第二个时钟滴答时,位B1右移并存储到FF中2出现在输出引脚Q处2而一个新的位,B2进入FF1。类似地,在每个时钟滴答时,寄存器内的数据向右移动一个比特,同时输入字的一个新比特进入寄存器。同时,可以在单个触发器输出处以并行方式提取存储在寄存器内的位。

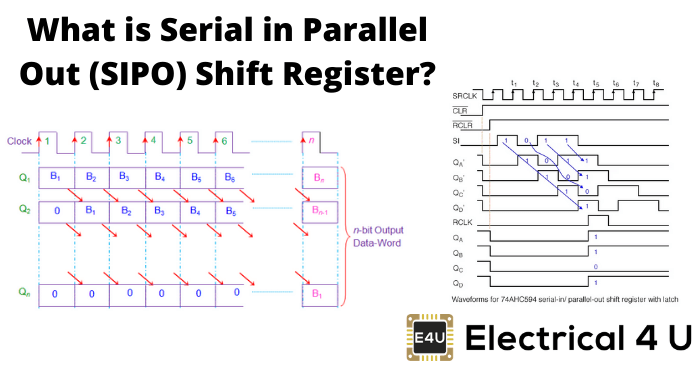

基于同样的理由分析,我们可以注意到n位输入数据字是作为n位输出数据字从n的上升边的移位寄存器获得的th时钟脉冲。移位寄存器的这种工作方式可以总结为表一,相应的波形如图2所示。

在右移SIPO移位寄存器中,数据位为每个时钟滴答而从左向右移位。然而,如果数据位在同一设计中从右向左移位,则会得到如图3所示的左移SIPO移位寄存器。然而,基本的工作原理保持不变,除了现在Bn到B1存储在Q中n去问1例如问1= B1,问2= B2……问n= Bn在nth时钟周期。