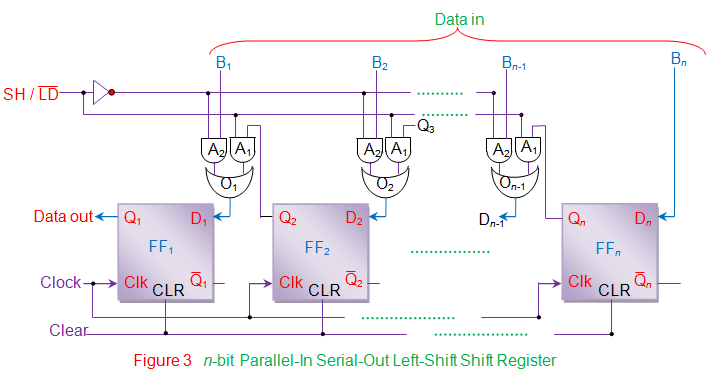

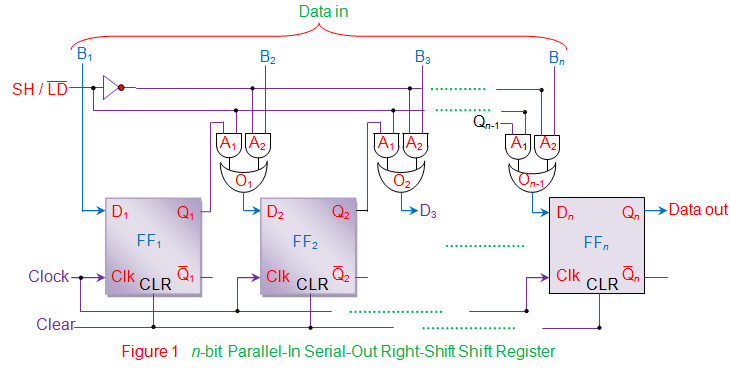

在在序列出(PISO)移位寄存器中并行,数据以并行格式加载到寄存器上,同时从其串行检索。图1显示了一个PISO移位寄存器有一个控制线 和组合电路(和或门)除基本寄存器组件外(人字拖)用时钟和清晰的针脚喂食。

和组合电路(和或门)除基本寄存器组件外(人字拖)用时钟和清晰的针脚喂食。

这里 控制线用于在给定的时间内的速度或负载中选择移位寄存器的功能。这是因为什么时候

控制线用于在给定的时间内的速度或负载中选择移位寄存器的功能。这是因为什么时候 线条低,a2和盖茨所有组合电路都变得活跃,而a1盖茨变得不活跃。

线条低,a2和盖茨所有组合电路都变得活跃,而a1盖茨变得不活跃。

因此,显示为栅极A的输入数据字(数据中)的比特2作为输出被传递或门在每个单独的组合电路。这使得数据的各个位将要加载/存储到时钟的第一前缘的外观上的相应触发器中(除了bit b之外1直接存储到ff中1在第一个时钟滴答)。这表示输入数据字的所有位存储到同一时钟滴答处的寄存器组件中。

下一个, 线路被驱动高,以激活栅极a1在禁止盖茨的组合电路的内容2。这会导致每个输出位拖鞋出现在驱动非常下一个触发器的栅极的输出(除了最后的触发器ff之外N)即ff的输出位1(Q.1)出现为输出或门1(O.1)连接到d2;问:2= O的输出2= D.3.等等。在此阶段,如果出现时钟脉冲的上升沿,则Q1出现在Q.2,问:2出现在Q.3.,...和qN-1出现在Q.N。

线路被驱动高,以激活栅极a1在禁止盖茨的组合电路的内容2。这会导致每个输出位拖鞋出现在驱动非常下一个触发器的栅极的输出(除了最后的触发器ff之外N)即ff的输出位1(Q.1)出现为输出或门1(O.1)连接到d2;问:2= O的输出2= D.3.等等。在此阶段,如果出现时钟脉冲的上升沿,则Q1出现在Q.2,问:2出现在Q.3.,...和qN-1出现在Q.N。

这一切都不是以一位存储在寄存器内的数据的右转。类似地,可以看出,对于施加的每个进一步的时钟脉冲,一位通过N的输出引脚退出PISO移位寄存器TH.触发器(数据出= qNFF.N),除了串行输出,这是什么。因此,需要n个时钟周期以获得整个n位输入数据字作为PISO移位寄存器的串行输出。

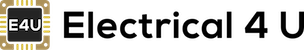

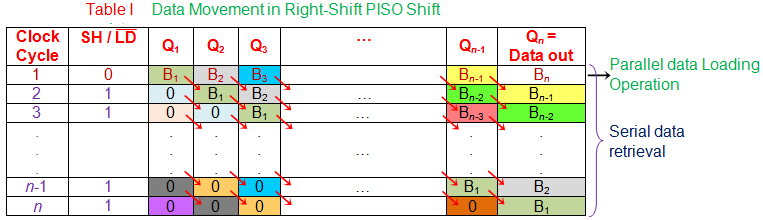

真相表PISO移位寄存器强调加载和检索过程由表I表示,而相应的波形由图2示出。

通过略微修改图1的设计,可以使寄存器内的数据位从左向左移动,从而获得左移PISO移位寄存器(图3)。然而,基本工作原则保持不变。