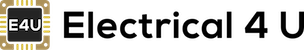

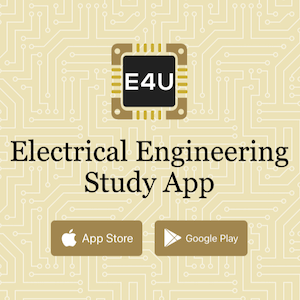

主奴隶触发器是两个触发器的级联组合,其中第一触发器中的第一触发器被指定为主触发器,而下一个被称为从触发器(图1)。这里,主触发器由外部时钟脉冲训练触发,而从站被激活在其反转中,即如果主站是正边缘触发的,则从站是负边缘触发,反之亦然。这意味着数据进入了触发器在时钟脉冲的前导/后缘,而在时钟脉冲的后缘/前沿在输出引脚处获得。因此,只有在一个全时钟脉冲的外观之后,才能完成其操作的主机触发器,它们也被称为脉冲触发的触发器。

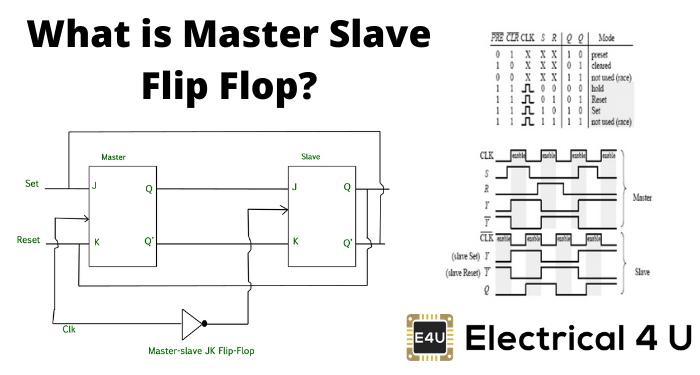

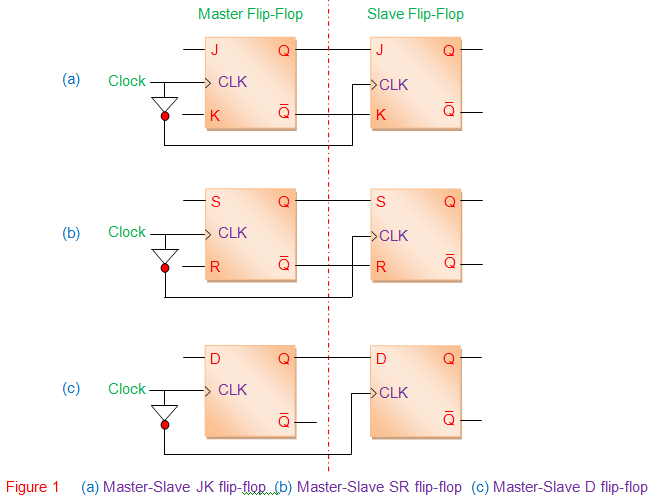

NAND门和逆变器的主机JK触发器域的内部结构和逆变器(以补充时钟信号)如图2所示。在这里可以看出NAND门1(n1)有三个输入,即外部时钟脉冲(clock)、输入J和输出Q̅;与非门2 (N2)具有外部时钟脉冲(时钟),输入k和输出Q作为其输入。

此外,n的输出1和n2盖茨作为克里斯交叉连接门N的输入连接3.和n4.。这四个栅栏在一起(n1,n2,n3.和n4.)形成触发器的主部分,而另外四个门的类似布置5.,n6.,n7.和n8.形成它的奴隶部分。

从图中,也很明显,奴隶由主设备的输出驱动(m1和M.2),符合其名称主奴隶触发器。此外,主站在时钟的正边缘期间是活动的1和M.2改变他们的州;根据j和k的值。但是此时,由于时钟脉冲的正边缘,从站将无效,整个系统(主从jk触发器)的输出保持不变。与此类似,从设备决定其输出Q和Q̅,具体取决于其输入M1和M.2,在主设备处于非活动状态的时钟的负边缘期间。

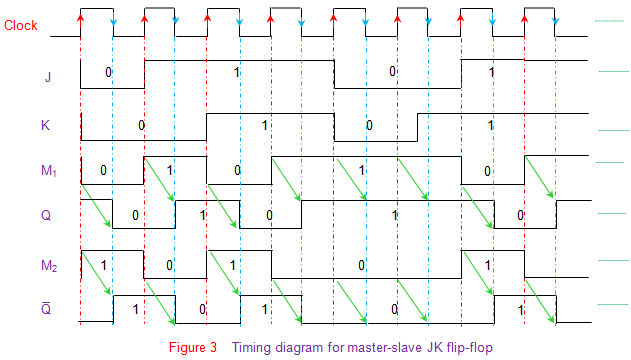

该真理表对应于工作的工作触发器如图2所示,由表I给出。这里可以看出,在时钟(红色箭头)的正边缘期间,触发器的主部分(括在红色框中的数据)的输出出现。但是此时,从站输出保持锁存或不变。在时钟脉冲(蓝色箭头)的负边缘期间,从器件将相同的数据传送到主从触发器(数据盒中括在蓝盒中)的输出引脚。在时序图中进一步强调了相同的原理主奴隶触发器由图3所示。在这里,绿色箭头用于指示从输出延迟的总时钟循环延迟。

此外,应注意,任何其他类型的主从触发器的工作类似于这里解释的主从jk触发器的工作。