内容

什么是JK触发器?

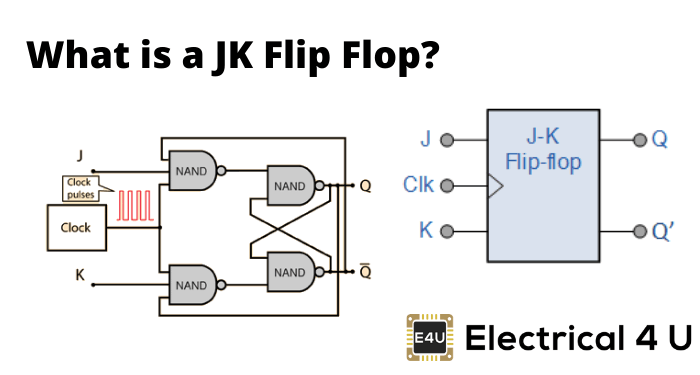

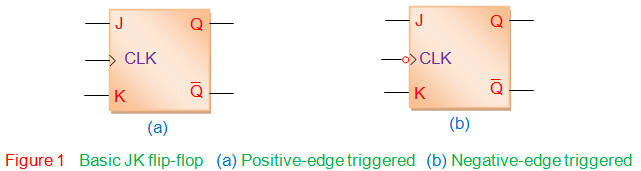

一种JK触发器是一个在其发明者之后命名的序贯双状态单位存储器设备杰克尔。通常,它具有一个时钟输入引脚(CLK),两个数据输入引脚(J和K),以及两个输出引脚(Q和Q̅),如图1所示.jk触发器可以在前缘触发时钟或其后缘上,因此分别可以是正面或负面触发的。

JK触发器电路

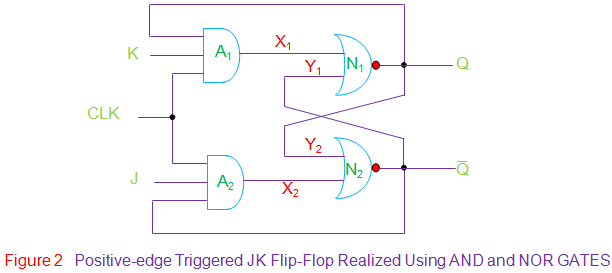

为了对JK触发器的工作有所了解,必须以类似于图2中的基本栅极来实现,这表达了正边缘触发的正边缘JK触发器使用和盖茨和也不是盖茨。

这里可以看到,输出Q与输入K和时钟脉冲(使用and门1,A1),输出Q̅与输入J和时钟脉冲(使用and门2,A2)。

进一步的输出1被馈送为一个输入(x1)到北1号NOR门1谁的其他输入(Y1)连接到输出Q̅。类似地,NOR门2,N2具有其两个输入(X2和Y2)作为输出2并输出Q(分别)。

初始设J = K = 0 Q = 0 Q̅= 1。现在考虑第一个时钟脉冲在CLK引脚的正边缘的出现触发器。这导致x1= 0和X2= 0。然后是N的输出1当X时变成01= 0和q̅= 1;虽然n的输出2将成为x2= 0和Q = 0.因此,一个得到Q = 0和Q̅= 1。

但是如果将初始状态视为j = k = 0,则q = 1和q∈= 0,则x1= X.2= 0导致Q = 1和Q̅= 0.这表明触发器输出Q和Q̅的状态对于J = k = 0的情况保持不变。

现在假设j = 0,k = 1,q = 0和q∈= 1.分析在同一个地面上,一个得到x1= X.2= 0进一步导致Q = 0(并且因此Q̅= 1)。对于同样的情况,如果q和q∈分别为1和0,则x1= 1和x2= 0将导致Q = 0(并且因此Q̅= 1)。

这意味着如果j = 0和k = 1,则触发器重置(q = 0和q̅= 1)。

如果J = 1, K = 0, Q = 1, Q̅= 0,则X1= X.2= 0,得到Q = 1(因此Q̅= 0)。同样的情况,如果Q = 0, Q̅= 1,则X1X = 0,2导致Q̅= 0的= 1,因此Q被强制为值1.这意味着对于j = 1和k = 0的情况,将始终设置触发器输出。q = 1和q∈= 0。

类似地,对于j = 1,k = 1,q = 1和q∈= 0一个得到x1= 1,x2= 0和q = 0(并且因此q̅= 1);如果q更改为0和q∈到1,则x1X = 0,2= 1迫使Q̅到0,因此Q到1。这表明对于J = K = 1,触发器输出切换意味着Q从0变化到1或从1变化到0,这些变化相应地反映在输出管脚Q̅。

然而,值得注意的是,如果时钟输入处没有上升沿,则触发器的状态保持不变。

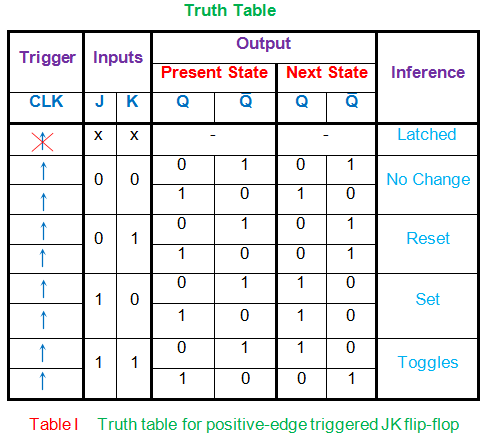

JK翻转翻转真值表

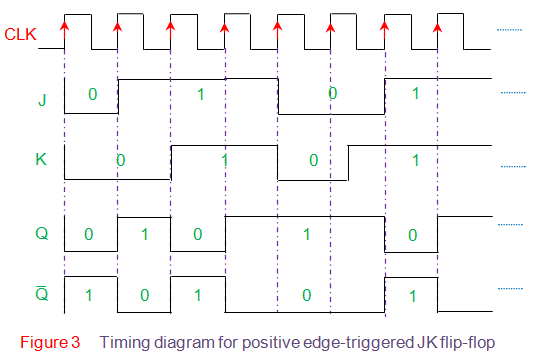

这真理表对于JK触发器,在下面的表I中已经总结了。与其有关的波形如图3所示。另外,要注意的是,负边缘触发的触发器的工作类似于正边缘触发的工作,除了改变发生在后缘时钟脉冲而不是其前沿。

JK触发器时序图

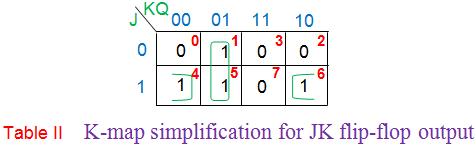

从上面的真相表可以到达输出的等式J K触发器(表二)时序图为JK触发器。

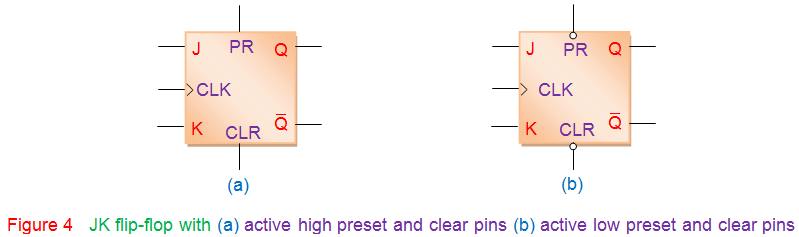

除了图1中显示的基本输入输出引脚外,j k触发器还可以具有特殊输入,如Clear(CLR)和预设(PR)(图4)。这些可用于将触发器从其当前状态带到明确状态。

例如,可以使用CLR引脚使输出等于0,而使用PR引脚将输出设为1。然而,这些引脚既可以有效的高(图4a)或有效的低(图4b)运行。

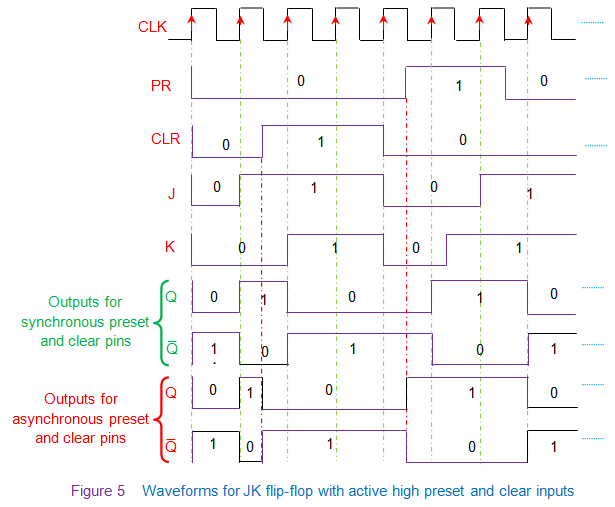

图5为有源高预置、清晰引脚的正边触发JK触发器波形。

此外,应该注意的是,这些引脚可以是同步的,其意味着清除和设定操作的含义,分别根据时钟(由绿线示出)或NO(由红线示出)。

此外,如果预设和透明引脚有效低,则在清除和预设速度而不是高电平时,图表中观察到的变化发生在瞬间。

也有D拖鞋那SR触发器那有效低SR触发器, 和门控SR触发器。

你可以通过查看我们的完整列表了解更多关于JK触发器和其他逻辑门逻辑盖茨问题。