什么是XOR门?

XOR门(也称为EOR或EXOR GATE) - 发音为独占或门 - 是一种数字逻辑门,当真正输入的数量是奇数时,一个数字逻辑门。XOR门实现一个独占的,即,如果一个 - 且只有一栅极的输入为真,则会发生真正的输出结果。如果两个输入都是假(即,低或0)或两个输入为真,则输出为false。

XOR表示不等式函数,即,如果输入不一样,则输出为真;否则,输出是假的。记住XOR的常见方式是“必须有一个或另一个,而不是两个”。

查看XOR门的另一种方法:二进制系统中的两个变量的模数如下所示:

逻辑门执行该模型和操作而不包括携带被称为XOR门。XOR门通常是两个输入逻辑门,其中输出仅是逻辑1当只有一个输入是逻辑1时。当两个输入相等时,均为1或两个都是0,输出将是逻辑0。

这就是一个原因XOR门也被称为抗巧合栅极或不等式探测器。这个门被称为XOR或独家或门因为当其输入完全1时,其输出仅为1。

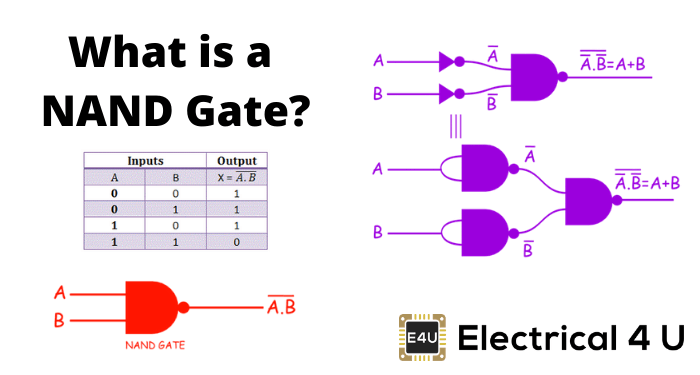

在数字电子产品,其他逻辑门包括不是盖茨那或门那NAND盖茨,和也不是盖茨。

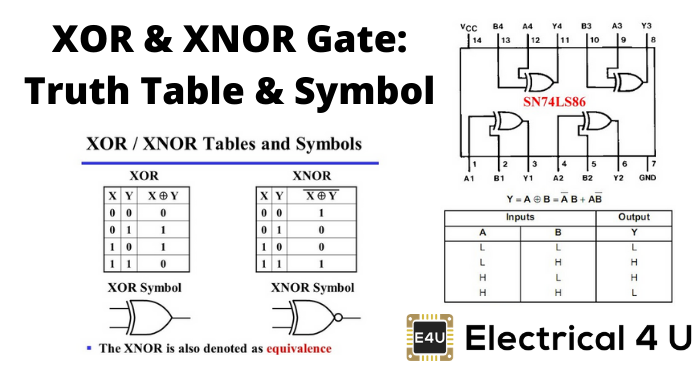

XOR门真相表

真理表列出特定数字逻辑电路的输出,以了解其输入的所有可能组合。该真相表XOR门如下:

上述真理表的二进制操作被称为独占或操作。它表示为△B.独占或操作的象征由由圆圈围绕的加号表示。

XOR门电路图

上面的表达式,可以简化为△B.

让我们证明上述表达式。

在第一次案例中,a = 0和b = 0。

在第二种情况下,a = 0和b = 1。

在第三种情况下考虑,a = 1和b = 0。

在第四种情况下,a = 1和b = 1。

所以证明了一个B的Boolean表达是AB +ÂB的,因为这种布尔表达式满足了所有输出状态相对于一个XOR门的输入条件。

从这种布尔表达式中,可以轻松实现XOR门的逻辑电路,这将如图所示,

XOR门的逻辑象征

XOR门逻辑地表示为,

多输入XOR门

虽然XOR门只能有两个输入,但您可以使用任意数量的输入执行XOR操作(例如,输入XOR操作或4输入XOR操作)。

两个以上的输入XOR操作是,当栅极区域1中的奇数数量时,输出为1,当没有或甚至输入的数量为1时,输出是逻辑0。

3输入XOR门

让我们实现具有三个输入A,B和C的XOR门。

现在,根据具有超过三个输入的XOR操作的定义,真相表将会,

这个真理表可以阐述,

从上述真相表中,发现三个二进制变量的XOR操作等同于一个变量的XOR操作,以及其他两个变量的XOR操作的结果。

从上面的真相表,

什么是Xnor门?

XNOR门(也称为Xorn't,Enor,Exnor或Nxor) - 并发音为独占式,也不是 - 是一种数字逻辑门,其功能是异或门(XOR门)的逻辑补充。逻辑上,一个xnor门是A.不是门其次是xor门。

输入A和B的XOR操作是A≠B;因此,XNOR操作这些输入将是(A + B)̅。这意味着XOR门的输出在Xnor门中反转。

在XOR栅极操作中,当仅一个输入为1时,输出仅为1。当两个输入都相同时,输出是逻辑0,这意味着它们是1或0。但在XNOR门中,逆为真。因此,当仅一个输入为0时,输出为0,并且当两个输入都相同时,输出为1(即两个0或两个1)。

请参阅下面的Xnor Gate Truth表中的视觉表示。

Xnor门真相表

该真相表当Xnor门如下所示:

逻辑XNOR操作由⊙表示。这是一个被圆圈包围的点。变量A和B之间的XNOR操作的表达式表示为⊙B。

现在,真相表对等式ab +Âb̅表示满意。

因此,证明了a⊙b= ab +Âb̅。通过使用可以证明同样的方法k-map.也。

XNOR门电路图

通过使用两个可以实现XNOR操作的表达不是盖茨,二和盖茨和一个人或门作为追随者,

Xnor门的符号:

3输入xnor门

像XOR门,Xnor门仅存有两个输入,但对于具有多个以上的输入的XNOR操作,我们必须使用多个Xnor门。

具有两个以上输入的XNOR操作就是这样。当高或逻辑1条件下有奇数输入时,输出将为0;否则,输出将为1。

现在,

从这个精心的真理表中,三个输入xnor门的逻辑符号可以表示为,

XOR门的应用

独家或门的主要应用正在运行半和全加法器。如果我们看看真相表仔细,我们会发现前三个结果完全满足过程二进制添加。仍然,在最后输入序列中,即,当输入都是1时,根据添加规则的结果应该是0,携带1.在真相表中,我们得到所需的0,但缺少1。

要在设计加法器的电路时解决此问题,请将AND AND添加到前或门在平行下。我们将详细展示加法器的电路。

从上图来看,我们可以看到两个输入通过在半加法电路中并行通过一个异或门和AND栅极。通过这个电路的操作,我们得到了总过程二进制添加顺利。

伪随机数生成- 模拟线性反馈移位寄存器,使用ex或栅极并生成随机的比特序列。